"Аюша-Z80" - CP/M-совместимый компьютер

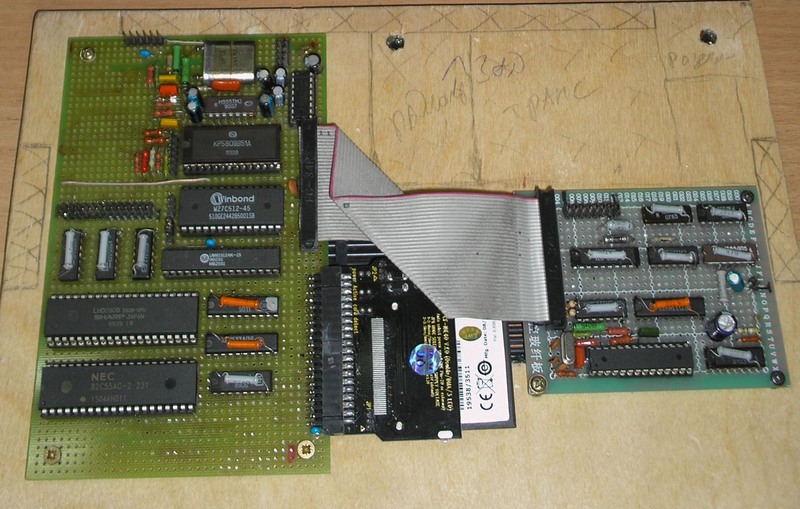

Прототип компьютера

USB-AT-PS/2 -> ASCII адаптер клавиатуры

Прошивки ПЗУ, операционной системы и контроллеров

Прототип компьютера. Сделан только один раз для испытания узлов в комплексе. Необязательно его повторять, но, если захочется, то... ;)

Схема основной платы компьютера "Аюша-Z80" приведена выше (кликабельно). Она содержит 12 микросхем, что меньше, чем в РК-86 ;), но больше чем у оригинальной конструкции Гранта Сирла (9 микросхем). Рассмотрим схему по узлам.

Тактовые импульсы на процессор могут поступать из двух источников. В полном варианте, с подключённым видеоадаптером, с последнего снимается тактовая частота 4 МГц. Если же процессорная плата используется самостоятельно, то дополнительный тактовый генератор собран на транзисторе КТ315 по схеме ёмкостной трёхточки с согласующим транзистором для ТТЛ-уровня, частота 2457,6 кГц. Генератор не выдаёт синусоиду или меандр, однако для Z80 это не имеет значения. Тактовые импульсы подаются далее на вход синхронизации D2, делитель на 4 D12, обеспечивающий тактовую частоту для последовательного порта D2, а также на джампер выбора тактовой частоты процессора D1. В обоих случаях тактовые импульсы проходят через элемент D7.1 с подтягивающим резистором 360 Ом для обеспечения требований к тактовым импульсам для Z80.

При настройке генератора необходимо подобрать сопротивление резистора 300К* в базовой цепи первого транзистора, добиваясь не только максимальной амплитуды, но и сдвига нижней границы выходного сигнала ближе к "нулю".

Процессор D1 подключен через шинные буферы, D3 шины адреса и D5 шины данных. Выбор в качестве адресных шинных формирователей микросхемы 1533АП4 объясняется потребляемым током - он в два раза меньше, чем у 1533АП6. Однако при повторении конструкции их можно заменить на АП6. Можно заметить, что в адресной шине буферизируются только младшие адреса, которые нагружены больше (особенно А0-А2), чем старшие (всего на два входа), а так как дальнейшего расширения системы не предвидится, то и второй буфер шины адреса было решено не ставить.

Поскольку входы CF-карты рассчитаны на уровни 5Вольт-КМОП, то осуществлена подтяжка сигналов /CS2, /IORD, /IORW и шины данных к плюсу питания. Резисторы на линиях D0-D1 шины данных расположены на плате видеоадаптера. Элементы D8.1, D7.1 и два транзисторных ключа обеспечивают выдачу на шину данных адреса FAH, необходимых при обработке прерывания типа IM2 (вектор процедуры обработки прерываний для СР/М расположен по адресу FFFAH; прерывания в мониторе работают в режиме IM1, обрабатываясь по вектору, расположенному по адресу 38Н). Диодное "или" на 1 ножке D5 обеспечивает процессору доступ к шине данных как в режиме чтения, так и в режиме считывания вектора прерывания. Также возможна подача на ножку инвертированного сигнала /WR, тогда сигнал /IM2 подключать к ней не нужно. Если буфер шины данных не будет устанавливаться, то и диодное "или" исключается из схемы.

На элементах микросхемы D9 собраны формирователи сигналов чтения/записи для ОЗУ и устройств ввода/вывода. Адресация устройств в/в осуществляется микросхемой D6. Используемые устройства и их адреса:

00Н-07Н - дисплей и клавиатура

08Н-0FH - 580ВВ51

10Н-17Н - CF-карта

18Н-1FH - резерв

20Н-27Н - резерв

28Н-2FH - резерв

30Н-37Н - 580ВВ55 - на схеме не показан, но в реале присутствует, подключение стандартное.

38Н-3FH - отключение ПЗУ в режиме СР/М

На элементах D7.3 и D7.2 собран триггер отключения ПЗУ (при активных сигналах /CS7 и /IOWR). В обычном режиме элемент D8.3 обеспечивает переключение между ОЗУ D11 и ПЗУ D10.

CF-карта подключена к процессорной плате через переходник IDE-CF, поэтому на схеме показана распиновка IDE-разъёма.

Последовательный порт D2 подключен по стандартной схеме. Связь с внешним миром осуществлена с помощью микросхемы МАХ232 (получаем упрощённый СОМ-порт).

Сброс системы обеспечивается триггером D14.1 аналогично узлу, применённому в компьютере "Специалист".

Джампер/переключатель страниц ПЗУ служит для выбора режима предзагрузки компьютера. При выборе первых 16К ПЗУ загружается простейший Монитор, позволяющий загружать программы в машинных кодах, встроенный Бейсик или ОС СР/М, при этом при включении выбирается активная консоль - видеоадаптер или последовательный порт. Первый режим служит в основном для загрузки нового программного обеспечения с внешнего компьютера. При выборе следующих 16К ПЗУ автоматически загружается ОС СР/М с активным видеоадаптером. Этот режим служит для повседневной работы с системой.

Дисплейный модуль и адаптер ASCII-клавиатуры расположены на отдельной плате, представляют собой самостоятельную конструкцию и описаны отдельно.

Общее потребление тока от источника питания 5 Вольт не превышает 800 мА.

Расположение процессорного модуля (слева) и дисплейного перед монтажом в корпус клавиатуры показано на фото. Между ними - адаптер IDE-CF.

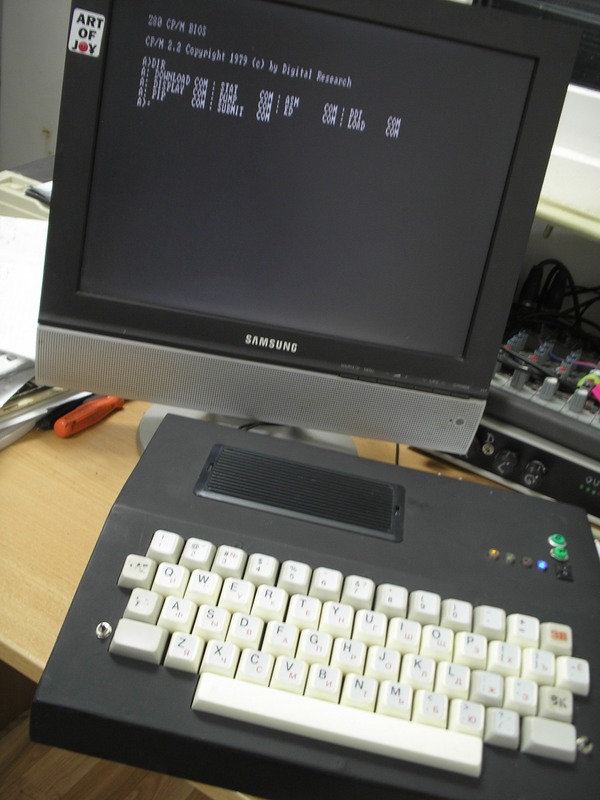

Вид загруженной ОС СР/М